# **Low-level Concurrent Programming Using the Relaxed Memory Calculus**

Michael J. Sullivan

CMU-CS-17-126 November 2017

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

**Thesis Committee:**

Karl Crary, Chair Kayvon Fatahalian Todd Mowry Paul McKenney, IBM

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Copyright © 2017 Michael J. Sullivan

This research was sponsored in part by the Carnegie Mellon University Presidential Fellowship. The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of any sponsoring institution, the U.S. government or any other entity.

#### **Abstract**

The Relaxed Memory Calculus (RMC) is a novel approach for portable low-level concurrent programming in the presence of the the relaxed memory behavior caused by modern hardware architectures and optimizing compilers. RMC takes a declarative approach to programming with relaxed memory: programmers explicitly specify constraints on execution order and on the visibility of writes. This differs from other low-level programming language memory models, which—when they exist—are usually based on ordering annotations attached to synchronization operations and/or explicit memory barriers.

In this thesis, we argue that this declarative approach based on explicit programmer-specified constraints is a practical approach for implementing low-level concurrent algorithms. To this end, we present RMC-C++, an extension of C++ with RMC constraints, and rmc-compiler, an LLVM based compiler for it.

#### Acknowledgments

It's difficult to overstate how much thanks is owed to my parents, Jack and Mary Sullivan. They've provided nearly three decades of consistent encouragement, support (emotional, moral, logistical, financial, and more), and advice ("Put 'write thesis proposal' on your To-Do List, then write the proposal and cross it off!"). I know I wasn't the easiest kid to raise, but they managed to mostly salvage the situation. Thank you—I wouldn't be here without you.

Thanks to my brother, Joey, who my interactions with over the years have shaped me in more ways than I understand. And I'm very grateful that—at this point in our lives—most of those interactions are now positive.

Immeasurable thanks to my advisor, Karl Crary, without whom this never would have happened. Karl is an incredible researcher and it was a pleasure to spend the last six years collaborating with him. Karl also—when I asked him about the CMU 5th Year Masters—was the one to convince me to apply to Ph.D. programs instead. Whether *that* is quite worth a "thanks" is a hard question to answer with anything approaching certainty, but I believe it is.

I also owe a great debt to Dave Eckhardt. Operating Systems Design and Implementation (15-410) is the best class that I have ever taken and I haven't been able to get it out of my head. The work I did over seven semesters as one of Dave's TAs for 410—teaching students about concurrency, operating systems, and, most of all, giving thoughtful and detailed feedback about software architecture and design—is the work I am most proud of, and I am supremely thankful for being able to be a part of it. While much of my work is likely to take me far afield, I try to carry a little of the kernel hacker ethic in my heart wherever I go. On top of that, Dave has been a consistent source of advice, support, and guidance without which I'd never have made it through grad school.

I owe much to a long string of excellent teachers I had in the Mequon-Thiensville School District, beginning with my third-grade teacher Mrs. Movall, who—in response to me asking if there was a less tedious way to draw some particular shape in LOGO—arranged for a math teacher to come over from the high school to teach me about the wonders of variables, if statements, and GOTOs. I owe a particularly large debt to Robin Schlei, who provided years of support, and to Kathleen Connelly, who first put me in touch with Mark Stehlik. Thank you!

On that note, thanks to Mark Stehlik, who was as good an undergraduate advisor as could be asked for, even if he wouldn't let me count HOT Compilation as an "applications" class. And thanks to all the great teachers I had at CMU, especially Bob Harper, who kindled an interest in programming languages.

Grad school was a long and sometimes painful road, and I'd have never made it through without my hobbies. Chief among them, my regular tabletop role-playing game group, who sacrificed countless Saturday nights to join me in liberating Polonia, exploring the Ironian Wastes for the Ambrosia Trading Company, and conclusively demonstrating, via their work for the Kromian Mages Guild, that not all wizards are subtle: Rhett Lauffenburger (Roger Kazynski), Gabe Routh (Hrothgar Boarbuggerer né Hrunting), Ben Blum (Yolanda Swaggins-Moonflute), Matt Maurer (Jack Silver), Michael Arntzenius (Jakub the Half-Giant), and Will Hagen (Daema). A GM couldn't ask for a better group of players. I'd also like to thank my other major escape: the EVE Online alliance Of Sound Mind, and especially the CEOs who have built SOUND into such a great group to fly with—XavierVE, June Ting, Ronnie Cordova, and Jacob Matthew Jansen.

Fly safe!

The SCS Musical provided another consistently valuable form of stress in my life, and I'd like to thank everybody involved in helping to revive it and keep it running. I had allowed myself to forget about the giant technical-theatre-shaped hole in my heart, and I don't think I'll be able to again.

Thanks to the old gang from Homestead—Becki Johnson, Gina Buzzanca, and Michael and Andrew Bartlein. Though we've been scattered far and wide from our parents' basements in Wisconsin—and though the Bartleins are rubbish at keeping in touch—you've remained some of my truest friends.

A lot of people provided—in their own ways—important emotional support at different points in the process. I owe particular thanks to Jack Ferris, Joshua Keller, Margaret Meyerhofer, Amanda Watson, and Sarah Schultz.

Salil Joshi and Joe Tassarotti contributed in important ways to the design of RMC and its compiler. Ben Segall, Paul Dagnelie, and Rick Benua provided helpful suggestions about benchmarking woes. Paul and Rick also provided useful comments on the draft. Matt Maurer provided some much needed statistical help. I'd like to thank Shaked Flur et al. for providing me with the ARMv8 version of the ppcmem tool, which proved invaluable for exploring the possible behaviors of ARMv8s.

A heartfelt thanks to everyone on my committee. Paul McKenney provided early and interesting feedback on this document (and a quote from "Sea Fever"), Kayvon Fatahalian gave excellent advice on what he saw as the key arguments of my work, and Todd Mowry helped me understand the computer architect's view of the world a little better.

I've had a lot of fantastic colleagues during the decade I spent at CMU, both as an undergrad and as a grad student. I learned more about computer science and about programming languages in conversation with my colleagues than I have from any books or papers. Thanks to Joshua Wise, Jacob Potter, Ben Blum, Ben Segall, Glenn Willen, Nathaniel Wesley Filardo, Matthew Wright, Elly Fong-Jones, Philip Gianfortoni, Car Bauer, Laura Abbott, Chris Lu, Eric Faust, Andrew Drake, Amanda Watson, Robert Marsh, Jack Ferris, Joshua Keller, Joshua Watzman, Cassandra Sparks, Ryan Pearl, Kelly Hope Harrington, Margaret Meyerhofer, Rick Benua, Paul Dagnelie, Michael Arntzenius, Carlo Anguili, Matthew Maurer, Joe Tassarotti, Rob Simmons, Chris Martens, Nico Feltman, Favonia, Danny Gratzer, Stefan Mueller, Anna Gommerstadt, and many many others.

Thanks also to all the wonderful colleagues I had working at Mozilla and Facebook on the Rust and Hack programming languages.

The most stressful and miserable part of my grad school process was the semester I spent preparing my thesis proposal. I was nearly burnt out after it and I don't think I could have kept on going without the ten weeks I spent "Working From Tahoe" (WFT) from The Fairway House in Lake Tahoe. Thanks to Vail Resorts and everybody who split the ski cabin with me for making it possible—especially to Jack Ferris and Kelly Hope Harrington for bullying me into it. And thanks to the Northstar Ski Patrol, the paramedics of the Truckee Fire Protection District, and the staff at the Tahoe Forest Hospital and the University of Pittsburgh Medical Center for all the excellent care I received after I skied into a tree.

Thanks to Aaron Rodgers and Mike McCarthy, but not to Dom Capers. Go Pack Go! NVIDIA Corporation donated a Jetson TK1 development kit which was used for testing and benchmarking. The IBM Power Systems Academic Initiative team provided access to a POWER8 machine which was used for testing and benchmarking.

To all of the undoubtedly countless people who I really really ought to have thanked here but who slipped my mind: I'm sorry, and thank you!

And last, but certainly not least, I'd like to extend a heartfelt thanks to Phil, Madz, Manny, and all the rest of the gang down at Emarhavil Heavy Industries. Emarhavil Heavy Industries—where there's always something big just over the horizon.

## **Contents**

| 1 | Intr | oduction | 1                                                    |

|---|------|----------|------------------------------------------------------|

|   | 1.1  | Sequen   | itial Consistency                                    |

|   | 1.2  | Paradis  | se Lost                                              |

|   |      | 1.2.1    | Hardware architecture problems                       |

|   |      | 1.2.2    | Compiler problems                                    |

|   | 1.3  | Langua   | age Memory Models                                    |

|   |      | 1.3.1    | Java                                                 |

|   |      | 1.3.2    | C++11                                                |

|   | 1.4  | A new    | approach                                             |

| 2 | The  | Relaxed  | l Memory Calculus                                    |

|   | 2.1  |          | of RMC                                               |

|   |      | 2.1.1    | Basics                                               |

|   |      | 2.1.2    | Concrete syntax: tagging                             |

|   |      | 2.1.3    | Pre and post edges                                   |

|   |      | 2.1.4    | Transitivity                                         |

|   |      | 2.1.5    | Pushes                                               |

|   | 2.2  | Examp    | le                                                   |

|   |      | 2.2.1    | Ring buffers                                         |

|   |      | 2.2.2    | Using data dependency                                |

|   | 2.3  | Advand   | ced Features                                         |

|   |      | 2.3.1    | Non-atomic locations and data races                  |

|   |      | 2.3.2    | Sequentially consistent locations                    |

|   |      | 2.3.3    | Give and take - fine-grained cross function edges    |

|   |      | 2.3.4    | LPRE and LPOST - Pre and Post edges to other actions |

|   | 2.4  | Model    | Details                                              |

|   |      | 2.4.1    | Execution Model                                      |

|   |      | 2.4.2    | Memory system model                                  |

|   | 2.5  | Discus   | sion                                                 |

|   |      | 2.5.1    | Execution vs. visibility                             |

|   |      | 2.5.2    | Recursion                                            |

| 3 | RM  | IC Formalism                                                   |   |       |     |   |   | 29 |

|---|-----|----------------------------------------------------------------|---|-------|-----|---|---|----|

|   | 3.1 | Basic RMC                                                      |   |       |     |   |   | 29 |

|   |     | 3.1.1 Syntax                                                   |   |       |     |   |   | 29 |

|   |     | 3.1.2 Thread static semantics                                  |   |       |     |   |   | 31 |

|   |     | 3.1.3 Thread dynamic semantics                                 |   |       |     |   |   | 32 |

|   |     | 3.1.4 The Store                                                |   |       |     |   |   | 34 |

|   |     | 3.1.5 Trace coherence                                          |   |       |     |   |   | 38 |

|   |     | 3.1.6 Store static semantics                                   |   |       |     |   |   | 39 |

|   |     | 3.1.7 Signature dynamic semantics                              |   |       |     |   |   | 40 |

|   |     | 3.1.8 Top-level semantics                                      |   |       |     |   |   | 41 |

|   | 3.2 | Discussion                                                     |   |       |     |   |   | 41 |

|   |     | 3.2.1 Mootness, incorrect speculation, and semantic deadlock . |   |       |     |   |   | 41 |

|   |     | 3.2.2 Read-read coherence                                      |   |       |     |   |   | 44 |

|   |     | 3.2.3 Connections to RMC-C++                                   |   |       |     |   |   | 44 |

|   |     | 3.2.4 Thin-Air Reads                                           |   |       |     |   |   | 48 |

|   | 3.3 | Metatheory                                                     |   |       |     |   |   | 50 |

|   |     | 3.3.1 Type safety                                              |   |       |     |   |   | 50 |

|   |     | 3.3.2 Sequential consistency results                           |   |       |     |   |   | 51 |

|   | 3.4 | Improvements and new features                                  |   |       |     |   |   | 52 |

|   | 5.1 | 3.4.1 Better compare-and-swap                                  |   |       |     |   |   | 52 |

|   |     | 3.4.2 Push edges                                               |   |       |     |   |   | 55 |

|   |     | 3.4.3 Spawning new threads                                     |   |       |     |   |   | 56 |

|   |     | 3.4.4 Liveness side conditions                                 |   |       |     |   |   | 57 |

|   |     | 3.4.5 Sequentially consistent operations                       |   |       |     |   |   | 58 |

|   |     | 3.4.6 Non-concurrent (plain) locations                         |   |       |     |   |   | 60 |

|   |     | 3.4.7 Allocations                                              |   |       |     |   |   | 63 |

|   |     | 5.4.7 Anocations                                               | • | <br>• | • • | • | • | 03 |

| 4 | Con | npiling RMC                                                    |   |       |     |   |   | 65 |

| • | 4.1 | General approach                                               |   |       |     |   |   | 65 |

|   | 4.2 | x86                                                            |   |       |     |   |   | 65 |

|   | 4.3 | ARMv7 and POWER                                                |   |       |     |   |   | 66 |

|   | 4.4 | Optimization                                                   |   |       |     |   |   | 68 |

|   |     | 4.4.1 General Approach                                         |   |       |     |   |   | 68 |

|   |     | 4.4.2 Analysis and preprocessing                               |   |       |     |   |   | 69 |

|   |     | 4.4.3 Compilation Using SMT                                    |   |       |     |   |   | 72 |

|   |     | 4.4.4 Scoped constraints                                       |   |       |     |   |   | 77 |

|   |     | 4.4.5 Finding data dependencies                                |   |       |     |   |   | 78 |

|   |     | 4.4.6 Using the solution                                       |   |       |     |   |   | 82 |

|   | 4.5 | _                                                              |   |       |     |   |   | 83 |

|   | 4.3 | ARMv8                                                          |   |       |     |   |   | 83 |

|   |     | •                                                              |   |       |     |   |   |    |

|   |     | $\mathcal{E}$                                                  |   |       |     |   |   | 84 |

|   |     | 4.5.3 Using dmb ld                                             |   |       |     |   |   | 85 |

|   | 4 - | 4.5.4 Faking lwsync                                            |   |       |     |   |   | 86 |

|   | 4.6 | Compilation weights                                            |   |       |     |   | _ | 86 |

|   | 4.7          | Sequentially consistent atomics     |

|---|--------------|-------------------------------------|

| 5 | e Studies 89 |                                     |

|   | 5.1          | Preliminaries                       |

|   |              | 5.1.1 Generation-counted pointers   |

|   |              | 5.1.2 Tagged pointers               |

|   | 5.2          | Treiber stacks                      |

|   |              | 5.2.1 RMC Version                   |

|   |              | 5.2.2 C++11 Version                 |

|   |              | 5.2.3 Discussion and Comparison     |

|   | 5.3          | Epoch-based memory management       |

|   |              | 5.3.1 Introduction                  |

|   |              | 5.3.2 Key epoch invariant           |

|   |              | 5.3.3 Core stuff                    |

|   |              | 5.3.4 RMC Implementation            |

|   | 5.4          | Michael-Scott queues                |

|   | 5.1          | 5.4.1 RMC Version                   |

|   |              | 5.4.2 C++11 Version                 |

|   | 5.5          | Queuing Spinlocks                   |

|   | 5.6          | Sequence locks                      |

|   | 5.0          | 5.6.1 RMC version                   |

|   |              | 5.6.2 C++11 Version                 |

|   |              | 5.6.3 Comparison                    |

|   | 5.7          | RCU-protected linked lists          |

|   | 5.7          |                                     |

|   |              |                                     |

|   | <b>5</b> 0   | 5.7.2 C++11 Version                 |

|   | 5.8          | An undergrad course project         |

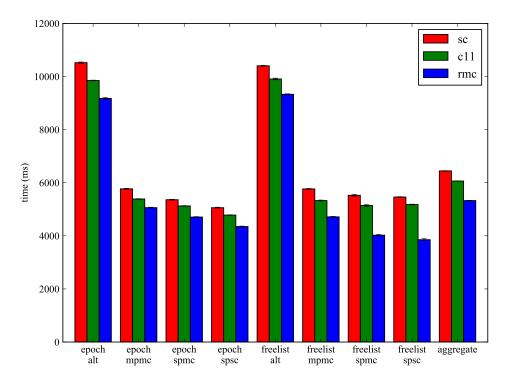

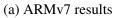

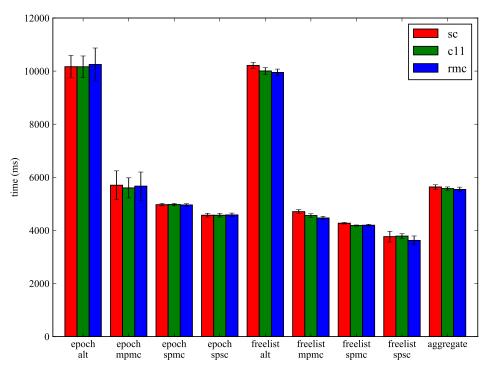

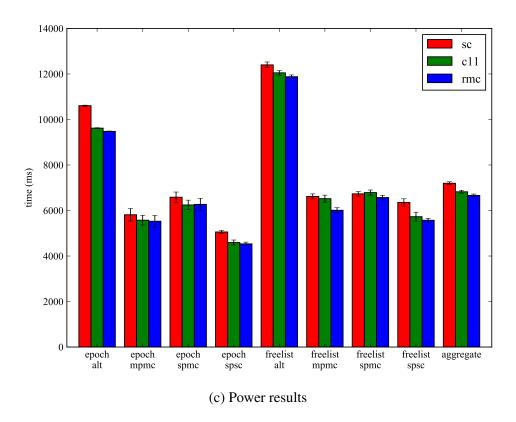

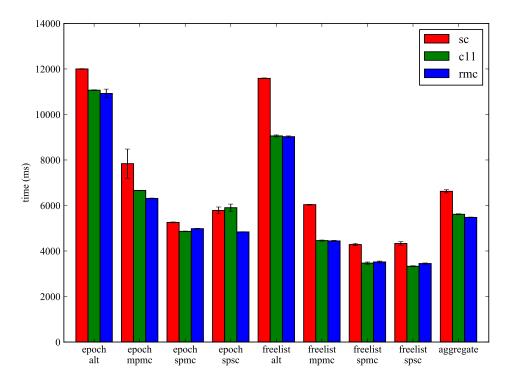

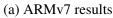

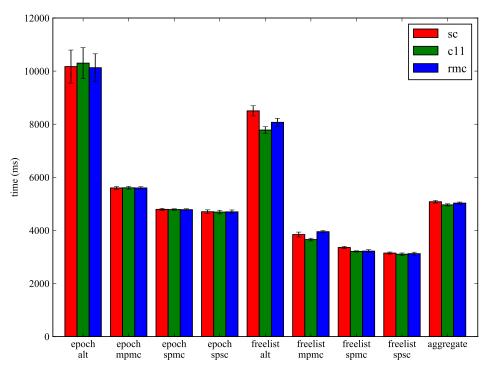

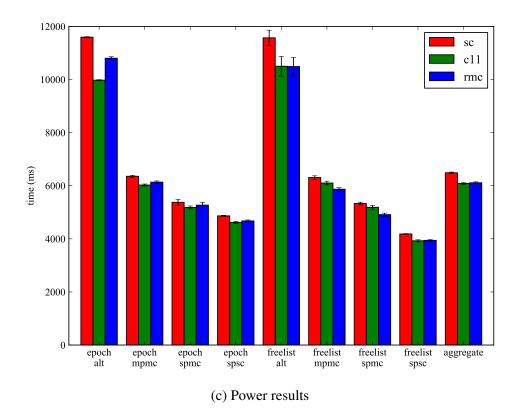

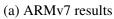

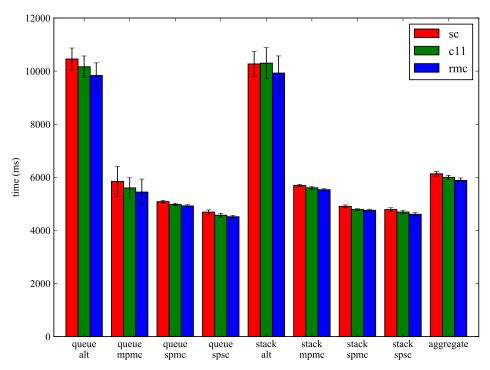

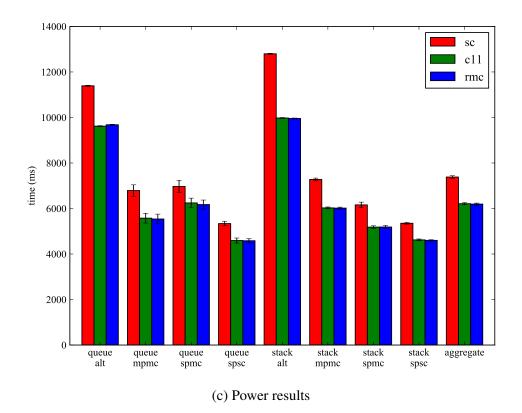

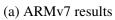

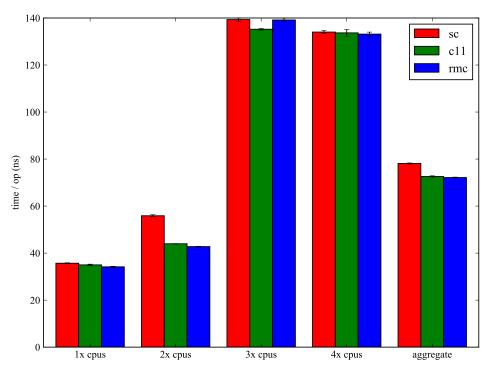

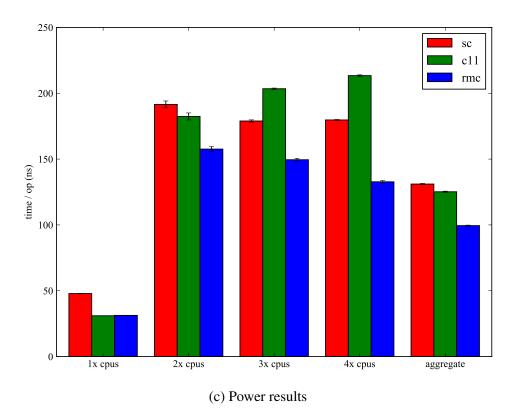

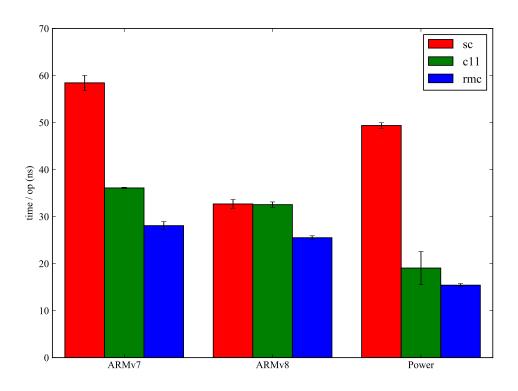

| 6 | Perf         | ormance Evaluation 119              |

|   | 6.1          | Generated code performance          |

|   | 6.2          | Compiler performance                |

| 7 | Con          | clusion 137                         |

| / |              |                                     |

|   | 7.1          | Usability                           |

|   | 7.2          | Performance                         |

|   | 7.3          | Related work                        |

|   | 7.4          | Future work                         |

| A | Full         | RMC recap 141                       |

|   | A.1          | Syntax                              |

|   | A.2          | Thread static semantics             |

|   | A.3          | Thread dynamic semantics            |

|   | A.4          | The Store                           |

|   | '            | A A 1 Synchronous store transitions |

| Bibliography |     |                                                     |             |  |  |  |  |

|--------------|-----|-----------------------------------------------------|-------------|--|--|--|--|

| В            |     | The proofs Sequential consistency for SC operations | 1 <b>53</b> |  |  |  |  |

|              |     | A.9.4 Thin-air                                      | .52         |  |  |  |  |

|              |     | A.9.3 Liveness                                      |             |  |  |  |  |

|              |     | A.9.2 Data races                                    | .52         |  |  |  |  |

|              |     | A.9.1 Mootness                                      | .52         |  |  |  |  |

|              | A.9 | Side conditions, etc                                | .52         |  |  |  |  |

|              | A.8 | Top-level semantics                                 | .51         |  |  |  |  |

|              | A.7 | Signature dynamic semantics                         | .51         |  |  |  |  |

|              | A.6 | Store static semantics                              | .50         |  |  |  |  |

|              | A.5 | Trace coherence                                     | 49          |  |  |  |  |

|              |     | A.4.3 Asynchronous store transitions                |             |  |  |  |  |

|              |     | A.4.2 Store orderings                               | .46         |  |  |  |  |

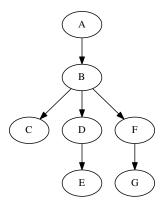

## Chapter 1

### Introduction

Writing programs with shared memory concurrency is notoriously difficult even under the best of circumstances. By "the best of circumstances", we mean something specific: when memory accesses are sequentially consistent. Sequential consistency promises that threads can be viewed as strictly interleaving accesses to a single shared memory [31]. Unfortunately, sequential consistency can be violated by CPU out-of-order execution and memory subsystems as well as by many very standard compiler optimizations.

Traditionally, languages approach this by guaranteeing that data-race-free code will behave in a sequentially consistent manner. Programmers can then use locks and other techniques to synchronize between threads and rule out data races. However, for performance-critical code and library implementation this may not be good enough, requiring languages that target these domains to provide a well defined low-level mechanism for shared memory concurrency. C and C++ (since the C++11 and C11 standards) provide a mechanism based around specifying "memory orderings" when accessing concurrently modified locations. These memory orderings induce constraints that limit the behavior of programs. The definitions here are very complicated, though, with lots of moving parts.

We propose a new, more declarative approach to handling weak memory in low-level concurrent programming based on the Relaxed Memory Calculus (RMC) [18]: explicit, programmer specified constraints. In RMC, the programmer explicitly specifies constraints on the order of execution of operations and on the visibility of memory writes.

#### 1.1 Sequential Consistency

Sequential consistency is the gold standard for compiling and executing concurrent programs that share memory [31]. An execution of a concurrent program is sequentially consistent if it is equivalent to executing some interleaving of execution of instructions from different threads, all accessing a single shared memory that maps from addresses to values. That is, threads run their code in order, sharing a single memory. While writing and reasoning about concurrent programs can still be quite difficult (because there can be many possible interleavings!), the model is easy to understand and much work has been put into developing tools and techniques for reasoning about it.

#### 1.2 Paradise Lost

#### 1.2.1 Hardware architecture problems

Modern multi-core architectures almost universally do not provide sequential consistency. The guarantees provided by different architectures, and the complexity of their respective models, can vary substantially. Intel's x86 architecture is very tame in the behaviors it allows and can be modeled in a fairly straightforward manner by considering each CPU to have a FIFO store buffer of writes that have not yet been propagated to the main memory [42]. Other architectures, such as POWER and ARM, have memory models so relaxed that most models [2, 40] dispense with the pleasant fiction of "memory" (a mapping from addresses to values) and instead work with a set of memory operations related by various partial orders.

One of the most common relaxed behaviors (and really the only one permitted on x86) is *store buffering*:

Here, two threads each write to a different shared variable, and then read from the variable that the other thread wrote to (this pattern is at the heart of some important theoretical mutual exclusion algorithms, like Dekker's algorithm [22]). Even though the writes appear before the reads, it is possible for neither thread to observe the other thread's write. Architecturally speaking, one way this could occur is if executing a write places it into a store buffer that is not flushed out to memory until later.

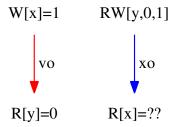

Another case to consider is message passing:

Here, one thread writes a message to the data location and then sets flag to indicate it is done; the other thread waits until the flag is set and reads the message. On x86 this code works as intended—r == 0 is not allowed. ARM, however, does allow r == 0. Architecturally speaking, one way this could occur is the processor executing instructions out of order. While both x86 and ARM have out-of-order execution, x86 takes pains to avoid getting caught in the act, and ARM does not.

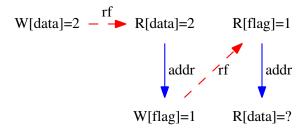

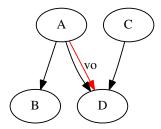

The examples discussed so far can be explained in a fairly straightforward way as the processor executing instructions out of order. This is insufficient to explain all of the behavior allowed by architectures such as POWER. For example, consider this variation on message passing (known as "WRC", for write-to-read causality), which we present diagrammatically as a graph of memory actions:

Here, we write "rf" to indicate a "reads-from" relationship between a write and a read and "addr" to indicate an address dependency. In this example, thread 0 writes to data, which is read by thread 1. Thread 1 then sets flag, which is read by thread 2, which subsequently reads from data. In order to ensure that the instructions are not reordered on by the processor, we insert address dependencies. If all weak memory effects came from the reordering of instructions, thread 2 would need to read 2 from data. On ARM and Power machines, however, it is possible for a write to become visible to different processors at different times—in this example, the write to data could become visible to thread 1 without becoming visible to thread 2.

This is an important point—relaxed memory can *not* be viewed simply as the result of the reordering of instructions, but must also incorporate a memory subsystem that can lead to weak behavior. One way of looking at it is that we must both account for the order of *execution* of instructions by the processor as well as the order in which writes become *visible* in the memory subsystem.

#### 1.2.2 Compiler problems

Although relaxed memory is commonly blamed on hardware, from a language perspective the compiler is arguably even more at fault. In particular, when compilers break sequential consistency, they generally do it even on single-processor machines (where multiple threads are interleaved based on a timer). A wide variety of compiler transformations that are totally valid in a single threaded setting violate sequential consistency. Worse still, many of these transformations are bread-and-butter optimizations: among them are common subexpression elimination, loop invariant code motion, and dead store elimination. Common subexpression elimination can break sequential consistency in a fairly straightforward way, if it can operate on memory reads:

Here, the second read from  $\star_p$  is changed to instead simply reuse the earlier read value, effectively reordering the second and third reads. The way that dead store elimination can break sequential consistency is a bit more subtle:

Here, the compiler sees that the first store to x is useless and eliminates it; this can allow another thread to observe the write to y without seeing the write to x that preceded it.

Loop-invariant code motion (loop hoisting) is particularly troublesome, because hoisting loop-invariant memory accesses can cause basically arbitrary reorderings of loads and stores.

There is another potential difficulty caused by loop hoisting, although it is arguably not a violation of sequential consistency:

```

int recv() {

while (!flag) {

continue;

}

return data;

}

int recv() {

if (!flag) {

while (1) continue;

}

return data;

}

```

Figure 1.1: Loop hoisting breaking things

By hoisting the load from flag, it becomes impossible for recy to exit the loop unless the initial read is true. While this is technically consistent with the thread never running again, and thus does not exhibit any behavior inconsistent with the threads interleaving, it is somewhat against the spirit of concurrent computation.

Something that the above examples all have in common is that they can only be detected if multiple threads concurrently access the memory involved, but that is not a necessary condition for an optimization to violate sequential consistency. The primary way to violate sequential consistency for code that is not otherwise racy is to introduce writes into code paths that would not otherwise have them, as in this transformation:

```

bool locked = mutex_trylock(&lock);

if (locked) successes += 1;

bool locked = mutex_trylock(&lock);

int increment = locked ? 1 : 0;

successes += increment;

```

Here, a conditional increment is rewritten into an unconditional one. In the original program, the successes variable is only written to if the attempt to lock the mutex succeeded. In the rewritten version, successes is always added to, but the value that is added depends on whether the lock succeeded. This introduces a data race (since successes is modified even when the lock was not taken); since += is generally implemented by reading the location, adding to it, and then writing it back (and not by an atomic operation), this transformation can allow increments of successes to be lost.

Compilers would be interested in this transformation because they can often use a conditional move instruction to select the value to add, avoiding the expense of an actual branch (which may be mispredicted). This optimization was actually performed by some versions of gcc before they walked it back under pressure from the Linux kernel development community [44].

#### 1.3 Language Memory Models

Writing lock-free code in a language without a memory model (like C and C++ until recently) is a fraught affair requiring knowledge of the particular hardware target as well as the specifics of what code the compiler might generate. Indeed, Linux's documentation for kernel programmers devotes significant space to these issues [25, 33]. Even code that scrupulously avoided any unsynchronized accesses could run afoul of the sort of write-inserting optimizations discussed above. In "Threads Cannot Be Implemented As a Library", Boehm persuasively argues that such an approach is untenable [10].

Language memory models attempt to tame this mess by providing a contract between the language implementer and users. Models provide language users with guarantees about how their code will behave and implementers with clarity about the boundaries of permissible optimization.

The starting point for most language memory models, such as Java's [32] and C++'s [12], is to focus on the common case of programs in which there are no *data races* ("concurrent conflicting accesses"). In this approach, the language requires that mutexes (and other concurrency primitives) be used to protect accesses to shared data. In exchange, the language promises that programs that do this will be sequentially consistent.

Some decision needs to be made about what semantics to give to programs that *do* still have data races. Generally, the idea is to give weak enough semantics that most traditional optimizations are still valid (as long as they avoid moving memory accesses past synchronization operations in unsafe ways). Typically, the common subexpression elimination, dead store elimination, and loop hoisting transformations shown in 1.2.2 are all valid, as only programs with data races could observe that changes. The branch elimination transformation, however, is not valid, since inserting the unconditional write to successes can introduce non-SC behavior in a program without data races.

This is a good starting point for a language memory model. Java and C++ both use it, as does RMC. Given this, there are two major questions left to answer when designing a language memory model: exactly what weak semantics to give programs with data races and what lower-level facilities to provide to allow programming that does not depend on locking everything. The latter question, in particular, will take us deep into the rabbit hole.

#### 1.3.1 Java

Java's answer for what facilities to provide for when mutexes are inappropriate is fairly simple and straightforward: locations declared as "volatile" can be safely accessed concurrently without being considered data races or forfeiting sequential consistency.

Java's story for what to do in programs with data races is substantially less straightforward, however. Java is a safe language that needs to provide some sort of semantics for incorrect (and even for overtly malicious) code. Java has struggled to provide a satisfactory answer here; as published its model prohibits some optimizations that are actually performed and allows some behaviors that were intended to be disallowed [5].

#### 1.3.2 C++11

C++'s answer for what semantics to give programs with data races is simple and very in the spirit of the language: none. Data races are now one of the numerous ways to invoke the specter of "undefined behavior" in C and C++ code.

The facilities provided by C++ for writing lock-free code, on the other hand, are multilayered and quite complicated. The highest level and simplest of these facilities that C++ provides are the *sequentially consistent atomics*—or *SC atomics*— that behave essentially like Java's volatile. The language with just locks and SC atomics admits an extremely clean and simple formalization: we need only consider potential sequentially consistent executions of the program, and if any of those have data races then the behavior is undefined.

Unfortunately, these SC atomics are fairly expensive to implement (requiring a fence for stores even on the extremely programmer friendly x86). Since many algorithms do not require the full guarantees of SC, C++ also provides various forms of *low-level atomics*. The general approach is to allow atomic memory operations to have a "memory order" specified; these memory orders determine what guarantees are provided. In order to model this more permissive system, C++, as is common, treats memory as a set of memory operations related by various partial orders. We will not delve into too much detail, but the most central of these orders is happens-before, which serves a key role in determining what writes are visible to reads. The happens-before relation, then, is best thought of as the transitive<sup>1</sup> closure of the union of program order and the synchronizes-with relation, which models inter-thread communication.

Other than "sequentially consistent", the tamest of these orders are "release" and "acquire". Release and acquire operations are not guaranteed to be sequentially consistent, but do allow threads to synchronize with each other in a fairly straightforward way: when an acquire operation reads from a release operation, a synchronizes—with relation holds between the operations, making any writes in the releasing thread visible in the acquiring one. A pair of simple functions to pass a message between two threads can be written using release and acquire:

```

int data;

std::atomic<int> flag;

void send(int msg) {

data = msg;

flag.store(1, std::memory_order_release);

}

int recv() {

while (!flag.load(std::memory_order_acquire))

continue;

return data;

}

```

All of the rest gets fairly hairy. The "relaxed" memory order is mostly useful for things like atomic counters and in conjunction with explicit memory fences. The explicit memory fences come in one variety for each of the memory orders (except consume and relaxed) and are intended

<sup>&</sup>lt;sup>1</sup>Although as we will see shortly, it is not *actually* transitive.

for porting old code and further optimizing the placement of memory barriers. The definition of fences is one of the most complicated bits of the model, and the behavior of the fences is often not as expected. In particular, it is not possible to use "sequentially consistent" fences to restore sequential consistency to a program using weaker memory operations.

The "consume" memory order behaves like "acquire", except that it only establishes a happens-before relationship with operations that are data-dependent on the consume operation. This feature is included because on many architectures (such as ARM), an address or data dependency in the receiving thread of a message passing idiom is sufficient to ensure ordering and is often much cheaper than issuing a barrier. Some algorithms critically rely on this property for efficiency. Unfortunately, it is also sort of a mess. First, the simple definition of happens-before given above needs to be changed to a much messier form to accommodate this behavior; worse, the new definition isn't transitive! Second, it is dangerous to bake in a syntactic notion of dependency into the semantics of a language. Compiler optimizations work very hard to optimize away unnecessary dependencies, which makes it difficult to preserve consume's guarantees. Consequently, most compilers currently implement consume as equivalent to acquire, sacrificing its potential performance wins. There are proposals by McKenney et al. to change the semantics of consume to be more realistically implementable, but nothing seems finalized yet [35, 36].

C++11's ordering annotations and—especially—fences are coarse-grained tools. Memory order annotations on memory accesses allow the establishment of one-to-many ordering constraints and fences allow the establishment of many-to-many constraints, but there is no way to establish ordering between two individual accesses. If—as we believe is natural—the programmer reasons about the code in terms of relative ordering, this requires the programmer to translate from this mental model to the coarse-grained facilities provided by C++. We believe this is work better left to a compiler.

#### 1.4 A new approach

The core philosophy of the Relaxed Memory Calculus (RMC) approach is that reasoning about the relative ordering of events is fundamental to reasoning about concurrent programming. In a sequentially consistent setting, one might reason about the message passing example as follows "If flag = 1 is visible, then data = 1 as well. Furthermore, a read that flag == 1 executes before r = data, so we must have r == 1." Since relative ordering of operations is the key concept of low-level concurrent programming, we believe it is natural to directly expose it in the language.

It turns out to be useful to draw some finer distinctions, so in RMC programmers explicitly specify constraints on both the order of visibility of memory writes and on the execution of operations. These constraints are then enforced by the compiler, which has a great deal of latitude in how to achieve them. Because of the very fine-grained information about permissible behaviors, this can allow the generation of more efficient code.

This leads us to our thesis statement: Explicit programmer-specified constraints on execution order and visibility of writes are a practical approach for low-level concurrent programming in the presence of modern hardware and compiler optimizations.

For our approach to be practical, it should have an implementation in a real programming language that is rigorous, usable, and efficient. To demonstrate this, we:

- Give a tutorial introduction to RMC-C++, an extension of C++ that provides low-level atomics controlled by explicit programmer-specified ordering constraints (Chapter 2).

- Show that RMC is *rigorous* and amenable to formal reasoning by laying out the formal definition of the RMC core calculus, which has been substantially revised and extended since its original publication (Chapter 3).

- Present rmc-compiler, our LLVM-based compiler for RMC-extended languages and discuss the compilation of RMC to x86, ARM, and POWER (Chapter 4).

- Argue that our approach is *usable* by presenting a collection of realistic lock-free data structures and other related low-level concurrent programs implemented in RMC-C++ (Chapter 5).

- Demonstrate our *efficiency* by evaluating the performance of RMC programs (Chapter 6).

## Chapter 2

## The Relaxed Memory Calculus

In this section, we give a tour of the Relaxed Memory Calculus (RMC), through the lens of its realization as an extension to C++. When we need to distinguish "RMC as realized as a C++ extension" from "RMC as a core calculus", we will sometimes refer to the former as RMC-C++.

Much of the material in this section is adapted or copied from "A Calculus for Relaxed Memory" by Karl Crary and myself [18].

#### 2.1 A Tour of RMC

#### **2.1.1 Basics**

The Relaxed Memory Calculus (RMC) is a different approach to low-level lock-free concurrent programming. In the RMC model, the programmer can explicitly and directly specify the key ordering relations that govern the behavior of the program.

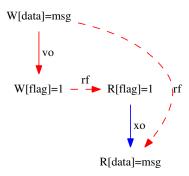

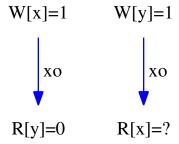

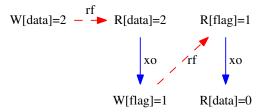

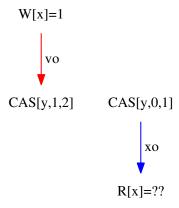

These key relations—which we will also refer to as "edges"—are that of *visibility-order* ( $\stackrel{\text{vo}}{\rightarrow}$ ) and *execution-order* ( $\stackrel{\text{xo}}{\rightarrow}$ ). To see the intended meaning of these relations, consider this pair of simple functions for passing a message between two threads:

The visibility edge  $(\stackrel{\text{vo}}{\rightarrow})$  between the writes in send ensures that the write to data is visible to other threads before the write to flag is. Somewhat more precisely, it means that any thread that can see the write to flag can also see the write to data. The execution edge  $(\stackrel{\text{xo}}{\rightarrow})$  between the reads in recv ensures that the reads from flag occur before the read from data does. This combination of constraints ensures the desired behavior: the loop that reads flag can not exit until it sees the write to flag in send; since the write to data must become visible to a thread first, it must be visible to the recv thread when it sees the write to flag; and then, since the read from data must execute after that, the write to data must be visible to the read.

Architectural aside: Having two actions ordered by visibility order most closely corresponds to requiring that they be separated by a Power-style "lightweight" sync (lwsync). A lightweight sync prevents instructions after it from being executed by the processor until all instructions before it have executed as well as preventing any writes after the sync from propagating to some other CPU until all writes that had propagated to the issuing CPU before the sync have propagated to that other CPU.

Having two actions ordered by execution order requires that something be done to prevent the instructions from being executed out of order on the CPU (in an observable way). On some architectures this could include the use of address or control dependencies as well as regular barriers.

On a Total Store Order machine such as the x86, nothing special need be done to enforce these orders. They always hold.

We can demonstrate this this diagrammatically as a graph of memory actions with the constraints as labeled edges:

In the diagram, the programmer specified edges ( $\stackrel{\text{vo}}{\rightarrow}$  and  $\stackrel{\text{xo}}{\rightarrow}$ ) are drawn as solid lines while the "reads-from" edges (written  $\stackrel{\text{rf}}{\rightarrow}$ ), which arise dynamically at runtime, are drawn as dashed lines. Since reading from a write is clearly a demonstration that the write is visible to the read, we draw reads-from edges in the same color red as we draw specified visibility-order edges, to emphasize that both carry visibility. Then, the chain of red visibility edges followed by the chain of blue execution order edges means that the write to data is *visible to* the read.

#### 2.1.2 Concrete syntax: tagging

Unfortunately, we can't actually just draw arrows between expressions in our source code, and so we need a way to describe these constraints in text. We do this by tagging expressions with names and then declaring constraints between tags:

```

int data;

rmc::atomic<int> flag;

int recv() {

void send(int msg) {

VEDGE(wdata, wflag);

L(wdata, data = msg);

L(wflag, flag = 1);

}

int recv() {

XEDGE(rflag, rdata);

while (!L(rflag, flag))

continue;

return L(rdata, data);

}

```

Here, the L construct is used to tag expressions. For example, the write data = msg is tagged as wdata while the read from flag is tagged rflag. The declaration VEDGE (wdata, wflag) creates a visibility-order edge between actions that are tagged wdata and actions tagged wflag. XEDGE (rflag, rdata) similarly creates an execution-order edge.

Visibility order implies execution order, since it does not make sense for an action to be visible before it has occured.

Visibility and execution edges only apply between actions in program order. This is mainly relevant for actions that occur in loops, such as:

```

VEDGE (before, after);

for (i = 0; i < 2; i++) {

L(after, x = i);

L(before, y = i + 10);

}</pre>

```

This generates visibility edges from writes to y to writes to x in future iterations, as shown in this trace (in which unlabeled black lines represent program order):

$$W[x]=0 \longrightarrow W[y]=10 \longrightarrow W[x]=1 \longrightarrow W[y]=11$$

Furthermore, edge declarations generate constraints between all actions that match the tags, not only the "next" one. If we flip the before and after tags in the previous example, we get:

```

VEDGE (before, after);

for (i = 0; i < 2; i++) {

L(before, x = i);

L(after, y = i + 10);

}</pre>

```

which yields the following trace:

$$W[x]=0 \longrightarrow W[y]=10 \longrightarrow W[x]=1 \longrightarrow W[y]=11$$

In addition to the obvious visibility edges between writes in the same loop iteration, we also have an edge from the write to x in the first iteration to the write to y in the second. This behavior extends to actions in future invocations of the function, as well. <sup>1</sup> This behavior will be important in the ring buffer example in Section 2.2.1.

While this behavior is a good default, it is sometimes necessary to have more fine-grained

<sup>&</sup>lt;sup>1</sup>Though *not* to actions in an overlapping recursive invocation of a function. See Section 2.5.2.

control over which matching actions are constrained. This can be done with "scoped" constraints: VEDGE\_HERE (a, b) establishes visibility edges between executions of a and b, but only ones that do not leave the "scope" of the constraint. <sup>2</sup> We can modify the above example with a scoped constraint:

```

for (i = 0; i < 2; i++) {

VEDGE_HERE(before, after);

L(before, x = i);

L(after, y = i + 10);

}</pre>

```

which yields the following trace in which the edges between iterations of the loop are not present:

$$W[x]=0 \longrightarrow W[y]=10 \longrightarrow W[x]=1 \longrightarrow W[y]=11$$

Because of annoying implementation details, L may only be used to tag expressions with values that can be assigned to a variable. To tag declarations, blocks, or calls to void functions, we provide LS (name, stmt);.

#### 2.1.3 Pre and post edges

So far, we have showed how to draw fine-grained constraint edges between actions. Sometimes, however, it is necessary to declare visibility and execution constraints in a much more coarse-grained manner. This is particularly common at library module boundaries, where it would be unwieldy and abstraction breaking to need to specify fine-grained edges between a library and client code. To accommodate these needs, RMC supports special pre and post labels that allow creating edges between an action and *all* of its program order predecessors or successors.

One of the most straightforward places where coarse-grained constraints are needed are in the implementation of locks. Here, any actions performed during the critical section must be visible to any thread that has observed the unlock at the end of it, as well as not being executed until the lock has actually been obtained. This corresponds to the actual release of a lock being visibility-order *after* everything before it in program order and the acquisition of a lock being execution-order *before* all of its program order successors.

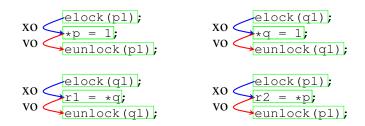

In this example implementation of simple spinlocks, we do this with post-execution edges from the exchange that attempts to acquire the lock and with pre-visibility edges to the write that releases the lock:

$<sup>^2</sup>$  Where the "scope" of a constraint is defined (somewhat unusually) as everything that is dominated by the constraint declaration in the control flow graph. Recall that a basic block A dominates B if every path from the entry point to B passes through A

```

void spinlock_lock(spinlock_t *lock) {

XEDGE(trylock, post);

while (L(trylock, lock->state.exchange(1)) == 1)

continue;

}

void spinlock_unlock(spinlock_t *lock) {

VEDGE(pre, unlock);

L(unlock, lock->state = 0);

}

```

#### 2.1.4 Transitivity

Visibility order and execution order are both transitive. This means that, although the primary meaning of visibility order is in how it relates writes, it is still useful to create edges between other sorts of actions.

In fact, because of this transitivity, it is even sometimes profitable to create edges to no-ops! In the <code>spinlock\_lock</code> example before, we draw an execution edge from <code>trylock</code> to the quasitag <code>post</code>. This means that each exchange on the lock is execution ordered before not only the body of the critical section, but, if the test-and-set fails, any future test-and-set attempts. This is stronger than is actually necessary, and we can weaken it using a no-op:

```

void spinlock_lock(spinlock_t *lock) {

XEDGE(trylock, acquired);

XEDGE(acquired, post);

while (L(trylock, lock->state.exchange(1)) == 1)

continue;

L(acquired, noop());

}

```

Here, the exchange is specified to execute before acquired, which is a no-op that is specified to execute before all of its successors. Since a no-op doesn't *do* anything, nothing is needed to ensure the execution order with the no-op, but transitivity ensures that the lock attempts are execution ordered before everything after acquired.

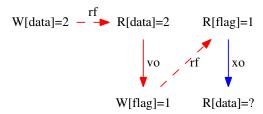

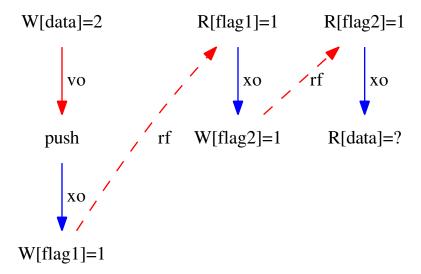

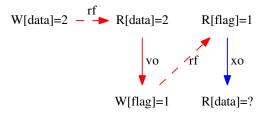

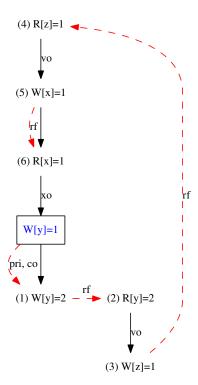

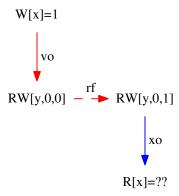

A somewhat more substantive and less niche application of transitivity of visibility occurs with visibility edges from reads to writes. Consider the following trace, a variant of the write-to-read causality example discussed earlier:

Since reads-from is a form of visibility, and since visibility is transitive, this means that W[data]=2 is visible before W[flag]=1. It is then also visibility ordered before R[flag]=1; since

that must execute before R[data]=?, this means that W[data]=2 must be *visible to* R[data]=?, which will then read from it.

#### **2.1.5 Pushes**

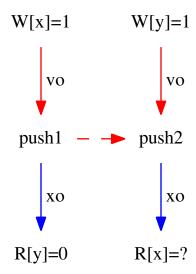

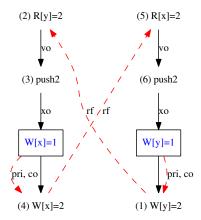

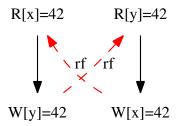

Visibility order is a powerful tool for controlling the *relative* visibility of actions, but sometimes it is necessary to worry about *global* visibility. One case where this might be useful is in preventing store buffering behavior:

Here, two threads each write a 1 into a memory location and then attempt to read the value from the other thread's location (this idiom is the core of the classic "Dekker's algorithm" for two thread mutual exclusion). In this trace, R[y] = 0 reads 0, and we would like to require (as would be the case under sequential consistency) that R[x] = ? will then read 1. However, it too can read 0, since nothing forces W[x] = 1 to be visible to it. Although there is an execution edge from W[x] = 1 to R[y] = 0, this only requires that W[x] = 1 executes first, not that it be visible to other threads. Upgrading the execution edges to visibility edges is similarly unhelpful; a visibility edge from a write to a read is only useful for its transitive effects, and there are none here. What we need is a way to specify that W[x] = 1 becomes visible before R[y] = 0 executes.

Pushes provide a means to do this: when a push executes, it is immediately globally visible (visible to all threads). As a consequence of this, visibility between push operations forms a total order. Using pushes, we can rewrite the above trace as:

Here, we have inserted a push that is visibility-after the writes and execution-before the read. Since visibility among pushes is total, either push1 or push2 is visible to the other. If push1 is visible before push2, as in the diagram, then W[x]=1 is visible to R[x]=?, which will then read 1. If push2 was visible to push1, then R[y]=0 would be impossible, as it would be able to see the W[y]=1 write.

In the concrete syntax, inserting a push takes the form of the simple but cumbersome:

```

VEDGE (write1, push1);

XEDGE (push1, read1);

L(write1, x = 1);

L(push1, rmc::push());

r = L(read1, y);

```

As a convenience, we provide the derived notion of "push edges". A push edge from an action a to b means that a push will be performed that is visibility after a and execution before b. More informally, it means that a will be globally visible before b executes.

```

PEDGE(write1, read1);

L(write1, x = 1);

r = L(read1, y);

```

**Architectural aside:** Pushes closely match "full" or "heavyweight" fences—MFENCE on x86, sync on Power, dmb on ARM. While in RMC terms, a push is an action that is visible to everything immediately, in an architectural sense, it is probably best thought of as an action that, when executed, stalls until all actions visible-before it have propagated to other threads.

Another, somewhat more unusual example of using pushes is:

Here, W[data]=2 is visibility before the push. Since the push executes before W[flag1]=1 and reads can only read-from writes that have already been executed, the push must execute before all of the other actions in this trace save the write to data. Since pushes are globally visible to all actions that execute after them, this means that the write to data is visible to the read from it, which must then return 2. If the push was elided and we merely had a visibility edge from W[data]=2 to W[flag1]=1, this would not be the case, and we would require a visibility edge between R[flag1]=1 and W[flag2]=1. Thus, pushes have stronger transitivity (or cumulativity) properties than just plain visibility edges do.

#### 2.2 Example

#### 2.2.1 Ring buffers

As a realistic example of code using the RMC memory model, consider the code in Figure 2.1. This code—adapted from the Linux kernel [26]—implements a ring buffer, a common data structure that implements an imperative queue with a fixed maximum size. The ring buffer maintains front and back pointers into an array, and the current contents of the queue are those that lie between the back and front pointers (wrapping around if necessary). Elements are inserted by advancing the back pointer, and removed by advancing the front pointer.

```

#define BUF_SIZE 1024 /* must divide the range of unsigned */

typedef struct ring_buf {

unsigned char buf[BUF_SIZE];

rmc::atomic<unsigned> front;

rmc::atomic<unsigned> back;

} ring_buf;

bool buf_enqueue(ring_buf *buf, unsigned char c) {

XEDGE(echeck, insert);

VEDGE(insert, eupdate);

unsigned back = buf->back;

unsigned front = L(echeck, buf->front);

bool enqueued = false;

if (back - front < BUF_SIZE) {</pre>

L(insert, buf->buf[back % BUF_SIZE] = c);

L(eupdate, buf->back = back + 1);

enqueued = true;

}

return enqueued;

}

int buf_dequeue(ring_buf *buf) {

XEDGE (dcheck, read);

XEDGE(read, dupdate);

unsigned front = buf->front;

unsigned back = L(dcheck, buf->back);

int c = -1;

if (back - front > 0) {

c = L(read, buf->buf[front % BUF_SIZE]);

L(dupdate, buf->front = front + 1);

}

return c;

}

```

Figure 2.1: A ring buffer

This ring buffer implementation is a single-producer, single-consumer, lock-free ring buffer. This means that only one reader and one writer are allowed to access the buffer at a time, but the one reader and the one writer may access the buffer concurrently.

In this implementation, we do not wrap the front and the back indexes around when we increment them, but instead whenever we index into the array. The number of elements in the buffer, then, can be calculated as back - front.

There are two important properties we require of the ring buffer: (1) the elements dequeued are the same elements that we enqueued (that is, threads do not read from an array location

Figure 2.2: Impossible ring buffer trace

without the write to that location being visible to it), and (2) no enqueue overwrites an element that has not been dequeued.

The key lines of code are those tagged echeck, insert, and eupdate (in enqueue), and dcheck, read, and dupdate (in dequeue). (It is not necessary to use disjoint tag variables in different functions; we do so to make the reasoning more clear.)

For property (1), the key constraints are insert  $\stackrel{\text{vo}}{\rightarrow}$  eupdate and dcheck  $\stackrel{\text{xo}}{\rightarrow}$  read. If we consider an dequeue reading from some enqueue, dcheck reads from eupdate and so insert  $\stackrel{\text{vo}}{\rightarrow}$  eupdate  $\stackrel{\text{rf}}{\rightarrow}$  dcheck  $\stackrel{\text{xo}}{\rightarrow}$  read. Thus insert is visible to read. Note, however, that if there are more than one element in the buffer, the eupdate that dcheck reads from will not be the eupdate that was performed when this value was enqueued, but one from some *later* enqueue. That is just fine, and the above reasoning still stands. As discussed above, constraints apply to *all* matching actions, even ones that do not occur during the same function invocation. Thus the write of the value into the buffer is visibility ordered before the back updates of all future enqueues by that thread.

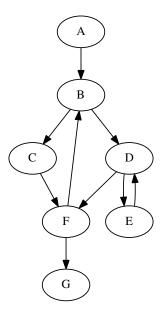

Property (2) is a bit more complicated. The canonical trace we wish to prevent appears in Figure 2.2. In it, read reads from insert, a "later" write that finds room in the buffer only because of the space freed up by dupdate. Hence, a current entry is overwritten.

This problematic trace is impossible, since read  $\stackrel{\text{xo}}{\rightarrow}$  dupdate  $\stackrel{\text{rf}}{\rightarrow}$  echeck  $\stackrel{\text{xo}}{\rightarrow}$  insert  $\stackrel{\text{rf}}{\rightarrow}$  read. Since you cannot read from a write that has not executed, writes must be executed earlier than any read that reads from them. Thus this implies that read executes before itself, which is a contradiction.

#### 2.2.2 Using data dependency

One of the biggest complications of the C++11 model is the "consume" memory order, which establishes ordering based on address and data dependencies (which we will generally lump together as "data dependencies"). This is useful because it allows read access to data structures

to avoid needing any barriers in many cases. This technique is extremely widespread in the Linux kernel. Some example code that could use this technique:

```

// A widget storing library

rmc::atomic<widget *> widgets[NUM_WIDGETS];

void update_widget(char *key, int foo, int bar) {

VEDGE(init, update);

widget *w = L(init, new widget(foo, bar));

int idx = calculate_idx(key);

L(update, widgets[idx] = w);

}

// Some client code

int use_widget(char *key) {

XEDGE_HERE(lookup, a);

int idx = calculate_idx(key);

widget *w = L(lookup, widgets[idx]);

return L(a, w->foo) + L(a, w->bar);

}

```

Here, we have a toy library for storing an array of widgets that tries to illustrate the shape of such code. In <code>update\_widget</code>, a new widget object is constructed and initialized and then a pointer is written into an array; to ensure visibility of the initialization, a visibility edge is used. In <code>use\_widget</code>, which is a client function to look up a widget and add together its two fields, the message passing idiom is completed by execution edges from the lookup to the actual accesses of the object. The use of <code>xedge\_here</code> is the one modification made in order to enable data dependencies—data dependencies can't enforce ordering with *all* subsequent invocations of the function, so we use <code>xedge\_here</code> so that the ordering only needs to apply within a given execution of the function. The key thing about this code is that it uses the same execution order idiom as message passing that does not have data dependencies—in RMC, we just provide a uniform execution order mechanism and rely on the compiler to be able to take advantage of existing data dependencies in cases like this one.

(Note that this code totally ignores the issue of freeing old widgets if they are overwritten. This is a subtle issue; the solution generally taken in Linux is the read-copy-update (RCU) mechanism [34].)

#### 2.3 Advanced Features

#### 2.3.1 Non-atomic locations and data races

While atomic memory operations in RMC come with extremely weak semantics (when unconstrained by visibility and execution edges), they still come with requirements that conflict with desired compiler optimizations, and so are too strong to credibly apply to *all* memory accesses. One such requirement is that each read reads the entire value from exactly one write: this can be invalidated when accessing large objects (which often need to be broken into several accesses)

or if updates to multiple objects are merged into a single memset or memcpy call. Another is the requirement that writes will eventually propagate out to all threads: as demonstrated in Figure 1.1, hoisting a read out of a loop can prevent it from ever observing a write.

While these assumptions are important when writing concurrent algorithms, they are a burden when compiling accesses that can't conflict with others. We thus adopt the same solution for RMC as vanilla C++11 adopts: we introduce a notion of *non-atomic* locations. These non-atomic locations are not allowed to be accessed concurrently, on pain of invoking undefined behavior (halt-and-catch-fire). By "accessed concurrently", we mean that there is a data race: two accesses to a location from different threads form a data race if at least one is a write and neither is visible-to the other. More details about data-races and the rationale for this definition can be found in Section 3.4.6.

In RMC-C++, locations are non-atomic by default. Making a location atomic is done at the type level, by declaring it as an rmc::atomic<T>.

Because the language makes *no* guarantees about the behavior of programs with racy accesses to non-atomics, *any* compiler transformation that is only detectable by programs with data-races on non-atomics is permitted: any program that can observe the different behavior induced by the transformation has a data-race on a non-atomic; since its behavior is therefore undefined, whatever behavior it observed is permissible.

#### 2.3.2 Sequentially consistent locations

#### Rationale

As discussed in Section 1.3.2, the C++11 model for concurrency has three different "levels" of mechanisms, each with increasing complexity and control: mutexes and other high level synchronization objects, sequentially consistent atomics, and low-level atomics.

While most of the focus of RMC—and most of the discussion in this document—has been on enabling low-level programming with fine-grained control a la C++'s low-level atomics, it is important that this be able to coexist with more coarse grained concurrent programming. RMC's story for incorporating locks is compelling and unsurprising—they can be implemented in RMC as shown in 2.1.3 and the compiler can generate efficient code.

Implementing something like C++'s sequentially consistent atomics—in which all operations on them have a total order—is also possible, although with some drawbacks. One implementation is:

```

void sc_store(rmc::atomic<int> *p, int val) {

PEDGE(pre, write);

L(write, *p = val);

}

int sc_load(rmc::atomic<int> *p) {

PEDGE(pre, read);

XEDGE(read, post);

return L(read, *p);

}

```

The pushes that occur before the loads and stores ensure that there is a push between any pair of SC operations. As shown in [18], this is sufficient to guarantee sequentially-consistent ordering between these actions. The execution post-edge from the load makes message passing through SC atomics work. The problem with this implementation is that the semantics it gives are *stronger* than necessary. In particular, this implementation requires that all previous memory operations are globally visible before an SC operation executes. This is stronger than is necessary—we need only that all of the other operations that we want to participate in the SC order be globally visible.

This is not merely a theoretical concern: C++'s SC atomics can be implemented on x86 as an MFENCE after stores and no fences at all on a load. The stronger RMC-style SC atomics presented above, however, require emitting an MFENCE before both loads and stores, which can be a substantial performance penalty. There are some other approaches for implementing SC atomics on top of already discussed RMC facilities, but all have similar problems.

#### Design

Once we have conceded that we actually need some kind of built in sequentially consistent operation, the high-level design is straightforward. At the language level, we simply introduce a new type of location, written rmc::sc\_atomic<T>, such that all operations on SC atomics participate in a total order of SC operations that is consistent with program order and is respected by reads (that is, reads read from the most recent write in the order). <sup>3</sup> Details about how this is achieved formally are discussed in Section 3.4.5. Additionally, so that sequentially consistent operations have the appropriate message passing semantics when interacting with weaker operations, all SC stores are implicitly visibility-after all earlier actions and SC loads are implicitly execution-before all later actions.

#### 2.3.3 Give and take - fine-grained cross function edges

#### **Motivation**

So far, we lack any kind of fine-grained support for constraint edges between different functions. Currently, ordinary point-to-point constraint edges can only be specified between two actions that appear inside the same function body. Thus, we are left with two rather indirect ways to impose edges between actions in different functions: place a label on an entire function invocation or use pre/post constraints. These are both very coarse-grained, however, and constrain all of the memory operations within the other function. This is fine for many situations, since most techniques for ensuring ordering are many-to-many or one-to-many, but some algorithms depend heavily on taking advantage of the point-to-point ordering guarantees provided by data dependence.

<sup>&</sup>lt;sup>3</sup>Another approach, which is actually the one taken in the core calculus, is to instead allow each individual operation to be tagged as either SC or not. We don't adopt this for our C++ version of RMC for several reasons—it complicates the programming model, it is probably generally not good practice to mix these access types anyways, and there have been correctness issues in C++11 regarding this sort of mixing that we would sooner avoid.

One example of this is the code presented in 2.2.2. That example is designed to demonstrate taking advantage of data dependencies, but the code is actually structured fairly poorly: use\_widget contains both the code for fetching the widget from the data structure and the code that uses the widget. This is unfortunate—we would rather write something like:

```

// Some library

widget *get_widget(char *key) {

int idx = calculate_idx(key);

return L(get_widget_lookup, widgets[idx]);

}

// Some client code

int use_widget(char *key) {

XEDGE(get_widget_lookup, a);

widget *w = get_widget(key);

return L(a, w->foo) + L(a, w->bar);

}

```

Here, the widget lookup is moved into a library function and a cross-function edge is drawn from the lookup to the uses of the widget. We do not, however, want to actually allow the direct specification of cross function edges: without them, RMC compilation is a per-function affair, which is a huge boon for efficient implementation.

#### **Approach**

Instead, we adopt the approach of considering the passing of an argument to a function or the returning of a value as a sort of pseudo-action that can be labeled and have edges drawn to it. We call these pseudo-actions "transfers". We write LGIVE (a, expr) to give a name to the passing of a value to another function and LTAKE (a, expr) to name the receipt of a value from another function. The above code would then be written as:

```

// Some library

widget *get_widget(char *key) {

XEDGE_HERE(get, ret);

int idx = calculate_idx(key);

widget *w = L(get, widgets[idx]);

return LGIVE(ret, w);

}

// Some client code

int use_widget(char *key) {

XEDGE_HERE(load_widget, a);

widget *w = LTAKE(load_widget, get_widget(key));

return L(a, w->foo) + L(a, w->bar);

}

```

Here, <code>get\_widget</code> looks up a widget by its id and returns it, but it uses <code>LGIVE</code> to specify that the loading of the widget ought to be execution order before returning it. Then, on the <code>use\_widget</code> side, we use <code>LTAKE</code> to indicate that reading out of the widget must execute after the transfer that returns the widget from <code>get\_widget</code>. By the transitivity of execution order, then, this gives us

that the load from widgets[idx] in get\_widgets must be execution-before the reads through w in use\_widget that consume its value.

It is important to note that LGIVE(a, expr) assigns a label to the act of passing the value of expr to another function (via a parameter or return value). It does *not* label the evaluation of expr. Thus it is necessary to separately label the actions producing a return value and the actual return and to link them up with constraints as needed.

We can also invert things, and draw an edge to the action of passing an argument to a function:

```

int consume_widget(widget *w) {

LTAKE(load_widget, w);

XEDGE_HERE(load_widget, ret);

return L(ret, w->foo);

}

int pass_widget() {

XEDGE_HERE(get, pass);

widget *w = L(get, widgets[0]);

return consume_widget(LGIVE(pass, w));

}

```

Here, note that we give a name to the receipt of a parameter by doing an LTAKE on the parameter name itself.

#### Rationale

One perhaps unusual thing is that while the focus of our examples was functions where the argument being passed is closely related to the actions that it is linked to, there is nothing fundamental that requires this. It is entirely possible to use a transfer to draw an edge between totally unrelated actions. If the mechanism is this general, why have the limitation of requiring that these pseudo-actions be connected to argument passing and value returning at all?

This design was chosen because it is a good match for the expected actual use cases of fine-grained cross-function edges: maintaining execution order between reading a pointer and reading through that pointer. In those cases, the edge really is closely connected to a value, and so directly associating it provides a very useful hint for both the programmer and the compiler.

#### 2.3.4 LPRE and LPOST - Pre and Post edges to other actions

In Section 2.1.4, we demonstrated combining transitivity and no-op actions in order to create a constraint from an action to everything that is program-order after some *other* point in the code. Explicitly using no-op actions is somewhat kludgy and syntactically heavyweight, so we provide LPRE and LPOST as conveniences around them. For example:

```

void spinlock_lock(spinlock_t *lock) {

XEDGE(trylock, critical_section);

while (L(trylock, lock->state.exchange(1)) == 1)

continue;

LPOST(critical_section);

}

```

LPRE and LPOST themselves are just simple macros that label a no-op action and give it either a pre- or post- visibility constraint:

```

#define LPRE(label) do { VEDGE_HERE(pre, label); L(label, noop()); } while(0)

#define LPOST(label) do { VEDGE_HERE(label, post); L(label, noop()); } while(0)

```

We always use visibility edges because visibility implies execution, which in the example above gives us transitive execution edges between trylock and everything after the LPOST. But edges to no-ops have no meaning on their own, so there are no real visibility constraints.

#### 2.4 Model Details

The model of how an RMC program is executed is split into two parts. On one side, the *execution model* models the potentially out-of-order execution of actions in the program. On the other side, the *memory system model* determines what values are read by memory reads.

Parts of the division of labor between the execution and memory system side in RMC are somewhat unusual for an operational model: the execution model is *extremely* weak and relies on the memory subsystem's coherence rules to enforce the correctness of single-threaded code.

#### 2.4.1 Execution Model

Intuitively, the model that we would like to have for how actions are executed, is that actions may be executed in any order at all, except as constrained by execution and visibility constraints. This includes when the actions have a dependency between them, whether control or data! That is, actions (both reads and writes) may be executed speculatively under the assumption that some "earlier" read will return a particular value.

Unfortunately, this extremely permissive model is *too* weak, and gives rise to problematic and bizarre behaviors known as "thin-air reads" in which writing a speculated value is eventually used to justify the read that produced it, in a sort of bizarre "stable time loop." <sup>4</sup> Unfortunately, while there exist recent systems that seem to solve this problem [29], they have not been incorporated into the RMC formalism yet. The situation is discussed in further detail in Section 3.2.4.

We are left for now, then, with the handways prose rule in from the C++14 standard: "Implementations should ensure that no 'out-of-thin-air' values are computed that circularly depend on their own computation." [28].

#### 2.4.2 Memory system model

The main question to be answered by a memory model is: for a given read, what writes is it permitted to read from? Under sequential consistency, the answer is "the most recent", but this is not a necessarily a meaningful concept in relaxed memory settings.

While RMC does not have a useful *global* total ordering of actions, there does exist a useful *per-location* ordering of writes that is respected by reads. <sup>5</sup> This order is called *coherence*

<sup>&</sup>lt;sup>4</sup>Like the song Johnny B. Goode in "Back to the Future"

Architectural aside: This is a direct consequence of cache coherence at the architectural level.

*order*. It is a strict partial order that only relates writes to the same location, and it is the primary technical device that we use to model what writes can be read. A read, then, can read from any write executed before it such that the constraints on coherence order are obeyed.

As part of RMC's aims to be as weak as possible (but not weaker), the rules for coherence order are only what are necessary to accomplish three goals: First, each individual location's should have a total order of operations that is consistent with program order (this is *slightly* stronger than just what is required to make single-threaded programs work.) Second, message passing using visibility and execution order constraints should work. Third, read-modify-write operations (like test-and-set and fetch-and-add) should be appropriately atomic.

The constraints on coherence order are the following:

- A read must read from the most recent write that it has seen—or from some other coherence-later write. More precisely, if a read A reads from some write B, then any other write to that location that is *prior to* A must be coherence-before B.

- If a write A is *prior to* some other write B to the same location, A must be coherence-before B.

- If a read-modify-write operation A reads from a write B, then A must *immediately* follow B in the coherence order. That is, any other write that is coherence-after A must also be coherence-after B.

An action A is *prior to* some action B on the same location if any of the following holds:

- A is earlier in program order than B. (This is crucial for making single threaded programs work properly.)

- A is visible to B.

- A and B are both sequentially-consistent operations and A was executed before B.

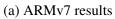

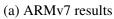

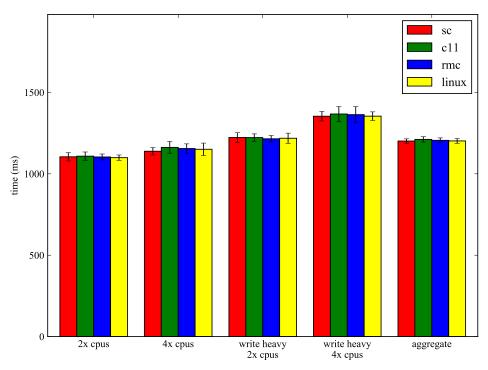

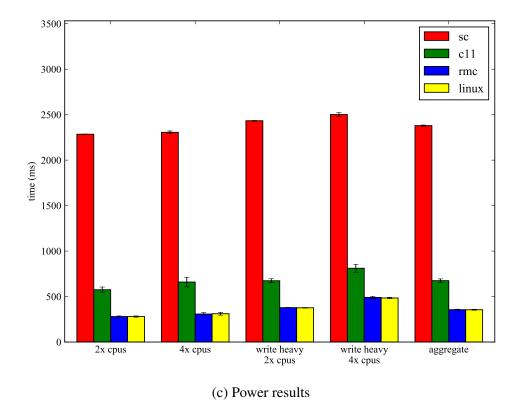

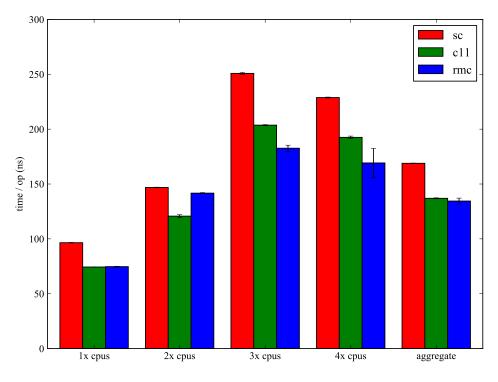

- A is transitively ordered before B by the previous three rules.